|

Tamaño: 2778

Comentario:

|

Tamaño: 3249

Comentario:

|

| Los textos eliminados se marcan así. | Los textos añadidos se marcan así. |

| Línea 3: | Línea 3: |

| * Valor inmediato de 32bits. * Registro de propósitos múltiples (en este caso se puede adicionar un corrimiento fijo o determinado por otro registro). |

* Valor inmediato de 32bits. * Registro de propósitos múltiples (en este caso se puede adicionar un corrimiento fijo o determinado por otro registro). |

| Línea 9: | Línea 10: |

| || {{{ Rm LSL {valor} }}} || El operador 2 (Rm) es desplazado un numero fijo de bits hacia la izquierda || || {{{ Rm LSL Rs }}} || El operador 2 (Rm) es desplazado Rs bits hacia la izquierda || Los tipos de desplazamientos son cinco y se describen a continuación: ||LSL||Corrimiento lógico hacia la izquierda||<img src="%ATTACHURL%/LSL.png">|| ||LSR||Corrimiento lógico hacia la derecha||<img width="85%" alt="LSR.png" src="%ATTACHURL%/LSR.png">|| ||ASR||Corrimiento Aritmético hacia la derecha||<img width="85%" alt="ASR.png" src="%ATTACHURL%/ASR.png">|| ||ROR||Rotación hacia la derecha||<img width="85%" alt="ROR.png" src="%ATTACHURL%/ROR.png">|| ||ROX||Rotación hacia la derecha extendido o rotación usando acarreo||<img width="85%" alt="RRX.png" src="%ATTACHURL%/RRX.png">|| == Descripción de la estructura de una instrucción que posee el operador 2 == === 32 bits inmediato === ||31||30||29||28||27||26||25||24||23||22||21||20||19||18||17||16||15||14||13||12||11||10||09||08||07||06||05||04||03||02||01||00|| ||cond ||||||||0 ||0 ||1 ||opcode ||||||||S ||Rn ||||||||Rd ||||||||rotate_imm||||||||immed_8|||||||||||||||| |||||||||||||||||||||||||||||||||||||||||| Operador 2|||||||||||||||||||||||| === Corrimiento inmediato === ||31||30||29||28||27||26||25||24||23||22||21||20||19||18||17||16||15||14||13||12||11||10||09||08||07||06||05||04||03||02||01||00|| ||cond ||||||||0 ||0 ||0 ||opcode ||||||||S ||Rn ||||||||Rd ||||||||shift_imm||||||||||tipo shift||||0||Rm|||||||| |||||||||||||||||||||||||||||||||||||||||| Operador 2|||||||||||||||||||||||| === Corrimiento por registro === ||31||30||29||28||27||26||25||24||23||22||21||20||19||18||17||16||15||14||13||12||11||10||09||08||07||06||05||04||03||02||01||00|| ||cond ||||||||0 ||0 ||0 ||opcode ||||||||S ||Rn ||||||||Rd ||||||||Rs||||||||0||tipo shift||||1||Rm|||||||| |||||||||||||||||||||||||||||||||||||||||| Operador 2|||||||||||||||||||||||| |

||{{{ Rm LSL {valor} }}} ||El operador 2 (Rm) es desplazado un numero fijo de bits hacia la izquierda || ||{{{ Rm LSL Rs }}} ||El operador 2 (Rm) es desplazado Rs bits hacia la izquierda || |

| Línea 47: | Línea 16: |

| Los tipos de desplazamientos son cinco y se describen a continuación: ||LSL||Corrimiento lógico hacia la izquierda||{{attachment:LSL.png | width="85%"}}|| ||LSR||Corrimiento lógico hacia la derecha||{{attachment:LSR.png | width="85%"}}|| ||ASR||Corrimiento Aritmético hacia la derecha||{{attachment:ASRL.png | width="85%"}}|| ||ROR||Rotación hacia la derecha||{{attachment:ROR.png | width="85%"}}|| ||ROX||Rotación hacia la derecha extendido o rotación usando acarreo||{{attachment:RRX.png | width="85%"}}|| == Descripción de la estructura de una instrucción que posee el operador 2 == === 32 bits inmediato === ||31 ||30 ||29 ||28 ||27 ||26 ||25 ||24 ||23 ||22 ||21 ||20 ||19 ||18 ||17 ||16 ||15 ||14 ||13 ||12 ||11 ||10 ||09 ||08 ||07 ||06 ||05 ||04 ||03 ||02 ||01 ||00 || ||||||||cond ||0 ||0 ||1 ||||||||opcode || S |||||||| Rn |||||||| Rd |||||||| rotate_imm |||||||||||||| immed_8 || ||||||||||||||||||||||||||||||||||||||||||<style="text-align: center;">Operador 2 ||||||||||||||||||||||<style="text-align: center;"> || === Corrimiento inmediato === ||31 ||30 ||29 ||28 ||27 ||26 ||25 ||24 ||23 ||22 ||21 ||20 ||19 ||18 ||17 ||16 ||15 ||14 ||13 ||12 ||11 ||10 ||09 ||08 ||07 ||06 ||05 ||04 ||03 ||02 ||01 ||00 || ||cond ||||||||<style="text-align: center;">0 ||0 ||0 ||opcode ||||||||<style="text-align: center;">S ||Rn ||||||||<style="text-align: center;">Rd ||||||||<style="text-align: center;">shift_imm ||||||||||<style="text-align: center;">tipo shift ||||<style="text-align: center;">0 ||Rm ||||||<style="text-align: center;"> || ||||||||||||||||||||||||||||||||||||||||||<style="text-align: center;">Operador 2 ||||||||||||||||||||||<style="text-align: center;"> || === Corrimiento por registro === ||31 ||30 ||29 ||28 ||27 ||26 ||25 ||24 ||23 ||22 ||21 ||20 ||19 ||18 ||17 ||16 ||15 ||14 ||13 ||12 ||11 ||10 ||09 ||08 ||07 ||06 ||05 ||04 ||03 ||02 ||01 ||00 || ||cond ||||||||<style="text-align: center;">0 ||0 ||0 ||opcode ||||||||<style="text-align: center;">S ||Rn ||||||||<style="text-align: center;">Rd ||||||||<style="text-align: center;">Rs ||||||||<style="text-align: center;">0 ||tipo shift ||||<style="text-align: center;">1 ||Rm ||||||<style="text-align: center;"> || ||||||||||||||||||||||||||||||||||||||||||<style="text-align: center;">Operador 2 ||||||||||||||||||||||<style="text-align: center;"> || |

Operador2

Es el segundo operador, que se encuentra en toda instrucción aritmética, lógica o de comparación este tiene características particulares, pudiendo ser:

- Valor inmediato de 32bits.

- Registro de propósitos múltiples (en este caso se puede adicionar un corrimiento fijo o determinado por otro registro).

Como se describió arriba, el operador 2 puede estar compuesto por un registro desplazado de una forma determinada (hacia la izquierda, derecha, corrimiento aritmético, etc) una cantidad fija de bits o dada por otro registro.

Describimos a continuación esta parte de la instrucción que se subdivide como una instrucción dentro de otra

Rm LSL {valor} |

El operador 2 (Rm) es desplazado un numero fijo de bits hacia la izquierda |

Rm LSL Rs |

El operador 2 (Rm) es desplazado Rs bits hacia la izquierda |

Los tipos de desplazamientos son cinco y se describen a continuación:

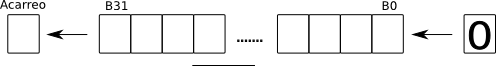

LSL |

Corrimiento lógico hacia la izquierda |

|

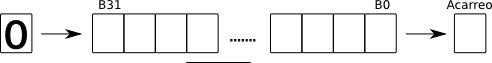

LSR |

Corrimiento lógico hacia la derecha |

|

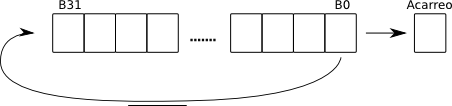

ASR |

Corrimiento Aritmético hacia la derecha |

|

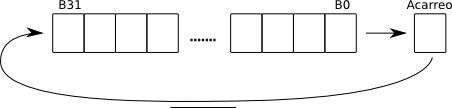

ROR |

Rotación hacia la derecha |

|

ROX |

Rotación hacia la derecha extendido o rotación usando acarreo |

|

Descripción de la estructura de una instrucción que posee el operador 2

32 bits inmediato

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

cond |

0 |

0 |

1 |

opcode |

S |

Rn |

Rd |

rotate_imm |

immed_8 |

||||||||||||||||||||||

Operador 2 |

|

||||||||||||||||||||||||||||||

Corrimiento inmediato

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

cond |

0 |

0 |

0 |

opcode |

S |

Rn |

Rd |

shift_imm |

tipo shift |

0 |

Rm |

|

|||||||||||||||||||

Operador 2 |

|

||||||||||||||||||||||||||||||

Corrimiento por registro

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

cond |

0 |

0 |

0 |

opcode |

S |

Rn |

Rd |

Rs |

0 |

tipo shift |

1 |

Rm |

|

||||||||||||||||||

Operador 2 |

|

||||||||||||||||||||||||||||||