# Conversores A/D de doble rampa y de doble rampa modificada

## Organización de la exposición:

- Introducción al tema

- Descripción de la operación del A/D

- Consideraciones de diseño

- Conclusiones

#### **Previamente:**

- Definición de especificaciones: Resolución, exactitud, monotonicidad, linealidad, etc.

- Criterio de muestreo

- Definición de circuito sample/hold y su diseño

- Conversores de rampa simple.

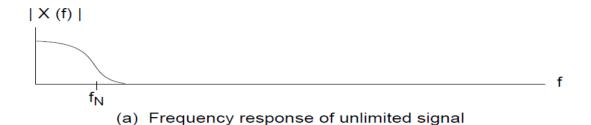

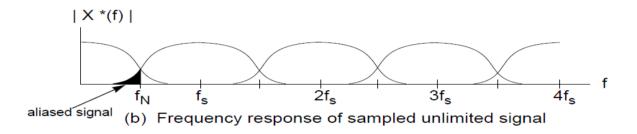

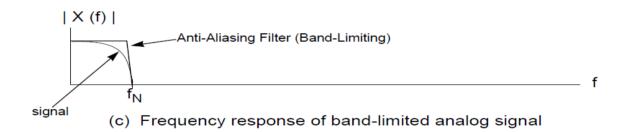

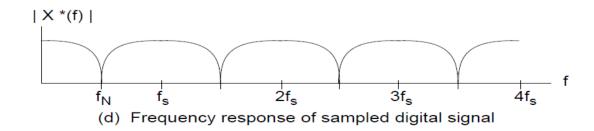

Una señal discreta puede ser escrita como:

Ec. 2.1

$$x*(t) = \sum_{n=-\infty}^{\infty} x(t)\delta(t-nT)$$

Donde:

$$\delta(t) = 1$$

para  $t = nT$

$$\delta(t) = 0$$

para todo otro t

El espectro se obtiene a partir de que  $\delta(t-nT)$  es una señal periódica con periodo T Entonces:

$$\sum_{n=-\infty}^{\infty} x(t)\delta(t-nT) = \frac{1}{T} \sum_{n=-\infty}^{\infty} x(t)e^{(j2n\pi t)/T}$$

Eqn. 2-2

Que puede ser escrita como:

$$x^*(t) = \frac{1}{T} \sum_{n=-\infty}^{\infty} x(t) e^{(j2n\pi t)/T} = \frac{1}{T} \sum_{n=-\infty}^{\infty} x(t) e^{j2\pi f} s^{nt}$$

Eqn. 2-3

Cortesía de Analog Devices, Inc. © 2005

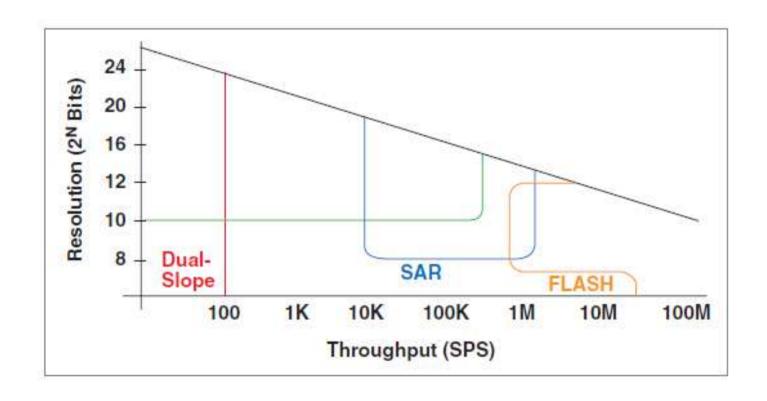

## Rango de aplicación de conversores A/D

© Microchip, Inc. (2008). Usado con autorización.

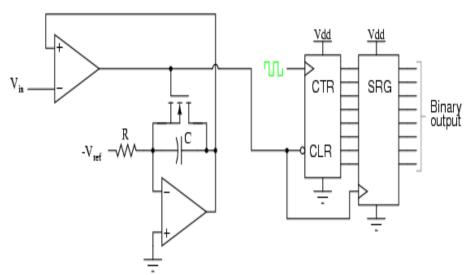

## Conversor de rampa simple:

## Ventajas:

- Bajo costo

- Alto rechazo de ruido (método integral)

#### **Limitaciones:**

- Alta sensibilidad a variaciones de componentes

- Fuerte dependencia de la estabilidad del reloj

- Problemas derivados de la polarización de dieléctricos con errores > a 1 bms en más de 10 bits

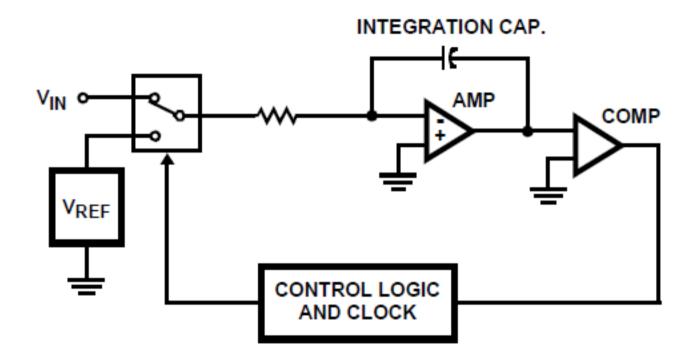

## Funcionamiento del conversor de doble rampa

## Operación del circuito

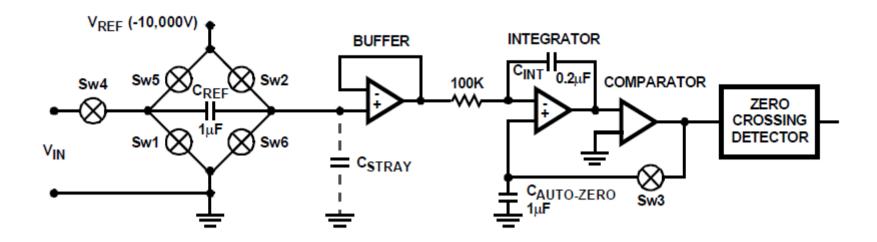

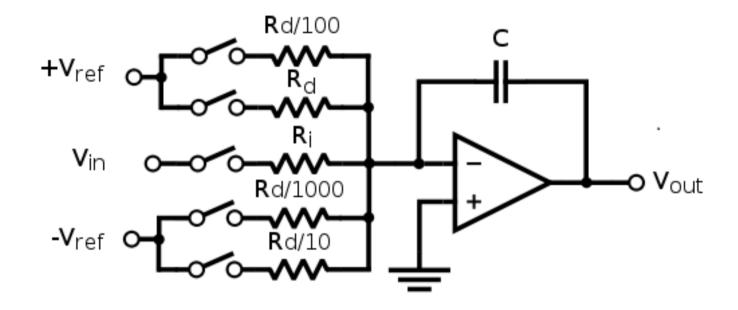

## Circuito analógico del A/D

Fase 1: Autocero.

- se eliminan los errores analógicos :

- se cierran sw1 y sw2

- se cierra sw3, guardando el offset total en C<sub>AZ</sub>

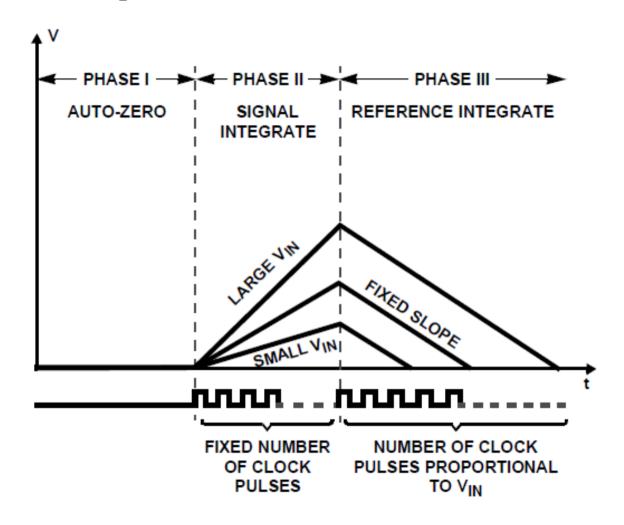

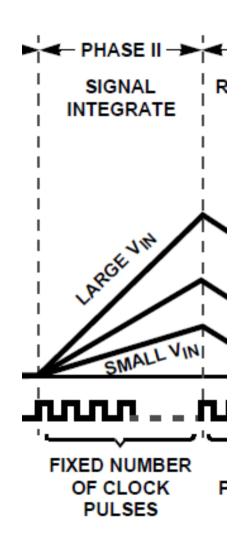

#### Fase II:

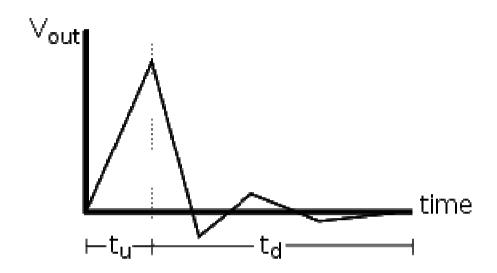

Se integra la señal de entrada durante un número fijo de periodos de reloj. Este número es típicamente 1000 para 3 ½ dígitos y 10000 para 4 ½ dígitos.

Se abren sw1,...,sw3 y se cierra sw4.

El valor final de la señal a la salida del integrador es proporcional a la tensión de entrada.

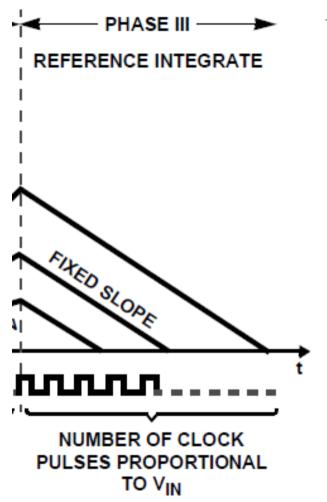

Fase III

Se abre sw4 y dependiendo de la polaridad de la señal, se cierran sw5 o sw6.

En cada caso, la rampa caerá con una pendiente proporcional a Vref.

El tiempo necesario para llevar V al valor de autocero es:

$$Nrac{V_{_{in}}}{V_{_{REF}}}$$

N: número de pulsos en fase II

Consideraciones de diseño:

En teoría, las fuentes de error son solo dos:

- estabilidad (jitter) de la frecuencia de reloj

- estabilidad de la referencia

Hoy las referencias de tiempo tienen errores menores a 1 ppm, por lo que, teóricamente, la calidad del sistema depende solo de la referencia.

#### Los errores reales se deben a:

- Variaciones en la tensión de los capacitores por pérdidas

- Cambio de las tensiones de los capacitores por causa de migración de cargas durante las transiciones de las llaves MOS.

- Alinealidades del búfer y del integrador

- Errores debidos a las limitaciones en alta frecuencia del búfer, integrador y comparador.

- Alinealidades en el capacitor del integrador por polarización

- Pérdidas de carga de C<sub>REF</sub> mientras carga C<sub>stray</sub>

1.- Variación de tensión en capacitores por pérdidas.

La pérdida en las llaves a valores de tensión normales es menor a 1 pA. La pérdida en las entradas de AOs con entrada MOS en menor a 2 pA.

Para reloj de 200 kHz y 10000 pulsos de integración, esto significa 0,83 µV en el circuito en consideración, resultando menor a 0,1 ppm del valor de referencia.

2.- Cambios en V<sub>C</sub> debidos a migración de cargas en las llaves

Los cambios en las tensiones de los capacitores por efecto de los cambios de estado de las llaves sólo son significativos en el grupo {sw1, sw2, sw5, sw6} y se minimizan usando técnicas de PWM para la conmutación.

## 3.- Alinealidades del búfer y del integrador

La contribución de este componente es muy baja: los amplificadores actuales tienen un comportamiento muy lineal de su RRMC y como la doble rampa compensa los valores en una y otra dirección, estos son muy pequeños pues el offset es similar en ambas.

4.- Errores debidos a las limitaciones en alta frecuencia del búfer, integrador y comparador.

Las transiciones del búfer ( $< 1 \mu s$ ) y del comparador ( $< 3 \mu s$  para 300 MHz de producto ganancia-ancho de banda) contribuyen con un error de ½ del bms. Esta es la contribución mas grande al error total.

5.- Alinealidades en el capacitor del integrador por polarización.

Los errores debidos a la polarización del dieléctrico del capacitor de integración se miden haciendo  $V_{in} = V_{ref}$ . Los menores errores se obtienen con capacitores de polipropileno, pues los efectos de variabilidad con la temperatura se corrigen en la doble rampa.

## 6.- Pérdidas de carga de C<sub>REF</sub> mientras carga C<sub>stray</sub>

El error introducido por una capacidad parásita de 15 pF en los impresos y demás genera, para valores positivos (los capacitores quedan en serie) un error de 15 ppm.

Para errores menores es necesario un cuidadoso diseño del CI para minimizar las capacidades parásitas.

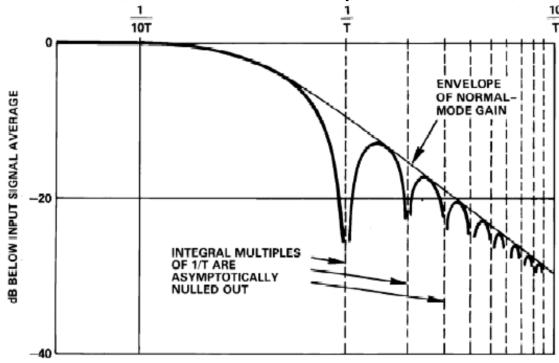

Efectos de la selección de la base de tiempos en relación a F línea

Se elige el valor de F<sub>reloj</sub> de modo tal que rechace las armónicas de la frecuencia de línea.

© Analog Devices Corp. 2008. Usado con autorización.

## Modificaciones al circuito previo.

## Conversores multirrampa

El defecto de largo tiempo de cuenta se minimiza a partir del uso de rampas múltiples.

El efecto de usar múltiples rampas implica reducir el número de ciclos de reloj necesarios para de- integrar el valor de entrada.

Usando el circuito de la figura anterior, se necesitan diez ciclos de reloj por cada dígito como máximo, en lugar de los 1000-10000 normales

La penalidad es la mayor complejidad del circuito de conmutación de las rampas.

#### Consideraciones de diseño.

La estructura de dos rampas implica el uso de capacitores de polipropileno. Existen capacitores de esta clase con errores menores al 1% (WIMA FKP2 p. ej.) (www.wima.de)

La cuidadosa distribución de componentes y el buen diseño de CI minimiza el valor de capacidades parásitas.

En la topología de múltiples rampas, para minimizar los errores de componentes, es recomendable el uso de resistores de 10 ppm, como los Vishay-Sfernice. (www.vishay.com)

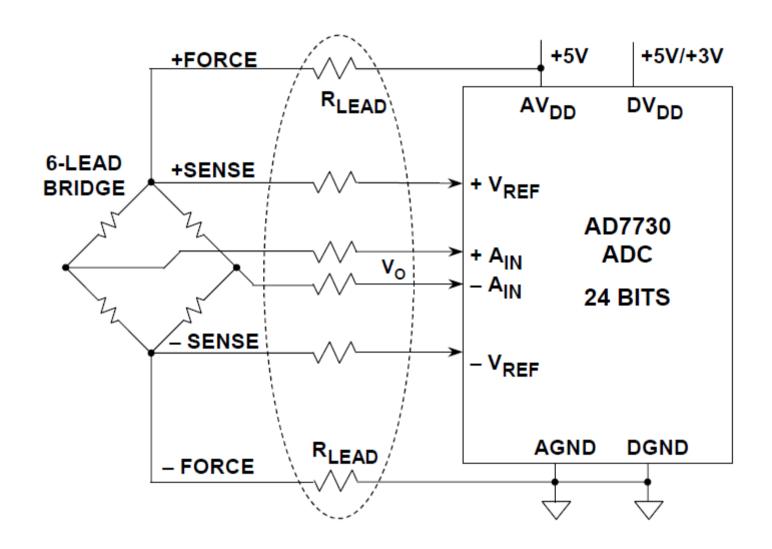

#### AD7730 Bridge Application (Simplified Schematic)

#### **Conclusiones:**

- El uso de conversores A/D de doble y múltiples rampas es recomendado en aplicaciones de alta perfomance (mas de 3 ½ digitos)

- Los errores asociados a la técnica pueden ser minimizados sin demasiadas complicaciones y sin elevar en demasía los costos.

- La limitación mas seria de la tecnología es su bajo rendimiento en tiempos, pues se consiguen en la práctica 20-30 muestras por segundo como máximo.

#### **Referencias:**

**Analog-Digital Conversion Handbook Analog Devices, Inc. 1986. Publicado por Prentice-Hall International**

**Analog Devices MT027 Tutorial "Integrating ADCs" Analog Devices, Inc. 2008**

The Integrating A/D Converter Intersil Americas, Inc. 2002

MicroChip Analog to Digital Design Guide Microchip Technology, Inc., 2005

MIT OpenCourseware®

6.004 Computation Structures

6.002 Circuits and Electronics

6.011 Introduction to Communication, Control and Signal Processing