|

Tamaño: 5457

Comentario:

|

Tamaño: 8029

Comentario:

|

| Los textos eliminados se marcan así. | Los textos añadidos se marcan así. |

| Línea 50: | Línea 50: |

| == Registros == || RBR || RO || 0x000 || Receiver Buffer Register. contiene el proximo byte a ser leido (DLAB = 0). || || THR || WO || 0x000 || Transmit Holding Register se escribe el proximo byte a enviar (DLAB = 0). || || DLL || R/W || 0x000 || Divisor Latch LSB. parte menos significativa del divisor (DLAB = 1). || || DLM || R/W || 0x004 || Divisor Latch MSB. parte mas significativa del divisor (DLAB = 1). || || IER || R/W || 0x004 || Interrupt Enable Register. contiene la habilitación de las 7 posibles fuentes de interrupción (DLAB = 0) || || IIR || RO || 0x008 || Interrupt ID Register. Interrupciones pendientes || || FCR || WO || 0x008 || FIFO Control Register. Controla la FIFO || || LCR || R/W || 0x00C || Line Control Register. Contiene el formato de del frame || || LSR || RO || 0x014 || Line Status Register. Contiene las banderas del estado de la transmisión y recepción || -CR R/W 0x01C Scratch Pad Register. Eight-bit temporary storage for software. 0x00 Table 933 ACR R/W 0x020 Auto-baud Control Register. Contains controls for the auto-baud feature. 0x00 Table 934 ICR R/W 0x024 IrDA control register (USART3 only) 0x00 Table 935 FDR R/W 0x028 Fractional Divider Register. Generates a clock input for the baud rate divider. 0x10 Table 937 OSR R/W 0x02C Oversampling Register. Controls the degree of oversampling during each bit time. 0xF0 Table 938 - - 0x030 - 0x03C Reserved - - HDEN R/W 0x040 Half-duplex enable Register - - 0x044 Reserved - SCICTRL R/W 0x048 Smart card interface control register 0x00 Table 940 RS485CTRL R/W 0x04C RS-485/EIA-485 Control. Contains controls to configure various aspects of RS-485/EIA-485 modes. 0x00 Table 941 RS485ADRMATCH R/W 0x050 RS-485/EIA-485 address match. Contains the address match value for RS-485/EIA-485 mode. 0x00 Table 942 RS485DLY R/W 0x054 RS-485/EIA-485 direction control delay. 0x00 Table 943 SYNCCTRL R/W 0x058 Synchronous mode control register. 0x00 Table 944 TER R/W 0x05C Transmit Enable Register. Turns off USART transmitter for use with software flow control. 0x01 Table 945 |

|

| Línea 86: | Línea 118: |

| donde fcr se deberá configurar de la siguiente forma | Donde fcr se deberá configurar de la siguiente forma |

| Línea 89: | Línea 122: |

| Todas estas acciones se realizan sobre el registro FCR, este registro es utilizado para configurar la FIFO, se muestra a continuación las distintas opciones que posee, extraído del manual del usuario | Todas estas acciones se realizan sobre el registro FCR, este registro es utilizado para configurar la FIFO, se muestra a continuación las distintas opciones que posee,(extraído del manual del usuario) |

| Línea 91: | Línea 124: |

| {{attachment:uart_fcr.png | "uart_fcr.png" | width="60%" }} | {{attachment:uartfcr_svg.png | "uartfcr_svg.png" | width="40%" }} * Habilitar la Transmisión {{{ STATIC INLINE void Chip_UART_TXEnable(LPC_USART_T *pUART); }}} === Uso de la UART === Una vez habilitada y en funcionamiento, se podrá enviar o leer los bytes recibido por medio de dos funciones de la LPCOpen * Enviar un byte {{{STATIC INLINE void Chip_UART_SendByte (LPC_USART_T *pUART, uint8_t data); }}} * Recibir un byte {{{STATIC INLINE uint8_t Chip_UART_ReadByte (LPC_USART_T *pUART);}}} |

Puertos Series (USART) en el microcontrolador LPC43XX con la biblioteca LPCOpen

Los periféricos USART (por sus siglas en ingles de Universal Synchronous/Asynchronous Receiver/Transmitter) son dispositivos de comunicación serie síncrona o asíncrona, que permite conectar el microcontrolador con otros equipos, obteniendo de esta forma un método simple para comunicar o recibir datos del exterior.

El LPC43xx posee 3 USART y 1 UART (solo permite el modo asíncrono) esta última con los pines necesarios para implementar una comunicación con un MODEM.

Lineas de comunicación

USART 0,2,3

Señal |

Descripción |

RxD |

Entrada |

TxD |

Salida |

DIR |

Utilizado en RS-485 y EIA-485 |

UCLK |

Clock para modo síncrono |

BAUD |

Solo disponible en USART3 para interfaz IrDA |

UART 1

Señal |

Descripción |

RxD |

Entrada |

TxD |

Salida |

CTS |

Clear To Send |

DCD |

Data Carrier Detect |

DSR |

Data Set Ready |

DTR |

Data Terminal Ready |

RI |

Ring Indicator |

RTS |

Request To Send |

UART (Universal Asynchronous Receiver/Transmitter)

EL modo de transmisión asíncrono (UART) corresponde a uno de los protocolos de comunicación serie mas difundidos, en este modo de transición los datos son enviados sin una señal de reloj externa.

Todas las UART del LPC43xx (las 3 USART funcionando en modo asíncrono y la UART) son compatibles con el estándar 550, esto significa que son compatibles con la UART diseñada por National Semiconductors 16550 y salida al mercado en 1987, esta UART reemplazaba a la 8250 primera interfaz serie de la PC XT.

En una transmisión asíncrona, los datos son divididos en palabras de una longitud fija, generalmente octetos, a los cuales se le agregan al comienzo códigos de sincronismo y luego al final del word se pueden agregar espacios, con lo cual permite al receptor identificar un nuevo código de sincronismo.

Como se comentó arriba, las palabras suelen ser octetos, este tipo de comunicación asíncrona se denomina orientada a caracter y uno de los estándar mas comunes es el RS-232 (Recommended Standard 232).

RS-232

El estándar RS-232 es una norma para el intercambio de datos entre dos dispositivos denominados DTE (Equipo terminal de datos) con un DCE (Equipo de comunicación de datos), A pesar de que este estándar soporta comunicación síncrona, su uso mas habitual es en comunicaciones asíncronas por ejemplo el implementado en una PC.

En el caso habitual de una PC llamaremos a la misma DTE, donde el DCE generalmente era el modem, en el caso de comunicarse dos PC entre si (DTE con DTE) no habrá modem, con lo cual la conexión se llamará Null Modem, en estos casos el cable que une las dos computadoras, debe unir las señales de manera cruzada, es decir por ejemplo que la señal denominada TxD en una de las PC debe unirse con la denominada RxD de la otra PC.

Registros

RBR |

RO |

0x000 |

Receiver Buffer Register. contiene el proximo byte a ser leido (DLAB = 0). |

THR |

WO |

0x000 |

Transmit Holding Register se escribe el proximo byte a enviar (DLAB = 0). |

DLL |

R/W |

0x000 |

Divisor Latch LSB. parte menos significativa del divisor (DLAB = 1). |

DLM |

R/W |

0x004 |

Divisor Latch MSB. parte mas significativa del divisor (DLAB = 1). |

IER |

R/W |

0x004 |

Interrupt Enable Register. contiene la habilitación de las 7 posibles fuentes de interrupción (DLAB = 0) |

IIR |

RO |

0x008 |

Interrupt ID Register. Interrupciones pendientes |

FCR |

WO |

0x008 |

FIFO Control Register. Controla la FIFO |

LCR |

R/W |

0x00C |

Line Control Register. Contiene el formato de del frame |

LSR |

RO |

0x014 |

Line Status Register. Contiene las banderas del estado de la transmisión y recepción |

-CR R/W 0x01C Scratch Pad Register. Eight-bit temporary storage for software. 0x00 Table 933 ACR R/W 0x020 Auto-baud Control Register. Contains controls for the auto-baud feature. 0x00 Table 934 ICR R/W 0x024 IrDA control register (USART3 only) 0x00 Table 935 FDR R/W 0x028 Fractional Divider Register. Generates a clock input for the baud rate divider. 0x10 Table 937 OSR R/W 0x02C Oversampling Register. Controls the degree of oversampling during each bit time. 0xF0 Table 938 - - 0x030 - 0x03C Reserved - - HDEN R/W 0x040 Half-duplex enable Register - - 0x044 Reserved - SCICTRL R/W 0x048 Smart card interface control register 0x00 Table 940 RS485CTRL R/W 0x04C RS-485/EIA-485 Control. Contains controls to configure various aspects of RS-485/EIA-485 modes. 0x00 Table 941 RS485ADRMATCH R/W 0x050 RS-485/EIA-485 address match. Contains the address match value for RS-485/EIA-485 mode. 0x00 Table 942 RS485DLY R/W 0x054 RS-485/EIA-485 direction control delay. 0x00 Table 943 SYNCCTRL R/W 0x058 Synchronous mode control register. 0x00 Table 944 TER R/W 0x05C Transmit Enable Register. Turns off USART transmitter for use with software flow control. 0x01 Table 945

Utilización de la USART del LPC43xx

Para implementar una interfaz serie RS-232, utilizaremos una USART en particular, la número 2, en la placa EDU-CIAA esta USART fue cableada al integrado FTDI2232, el mismo es el encargado de realizar la interfaz JTAG del microcontrolador y el USB, además de esta tarea, incorpora un puerto extra configurado en este caso como puerto serie asíncrono. Es en ese puerto donde se conecta los pines de la USART2 permitiendo realizar una muy sencilla conexión entre la PC y la EDU-CIAA.

Para la configuración de el puerto, se utilizará la librería LPCOpen

Configurar el SCU

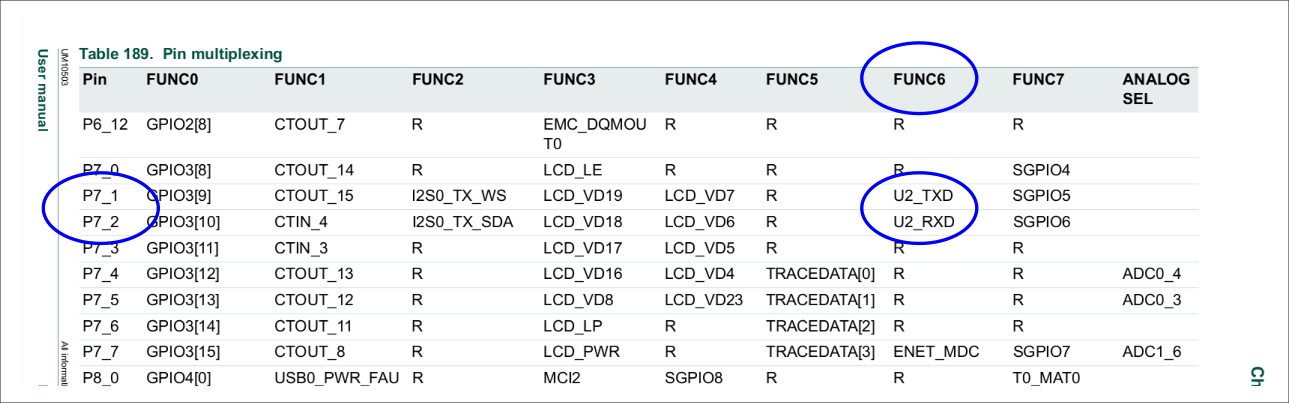

Se deben configurar los pines para ser usados por la USART, en su modo asincrónico solo utiliza dos señales RX y TX, estas serán las que se deberan configurar en la SCU.

Para evitar anular un dispositivo por ser requerido los pines para otra función, este microcontrolador mapea en varios pines cada linea de la USART, en el caso de la USART2 tenemos las siguientes opciones

U2_TXD |

en los pines P1_15, P2_10, P7_1, PA_1 |

U2_RXD |

en los pines P1_16, P2_11, P7_2, PA_2 |

En el momento de rutear la placa se eligió la dupla P7_1 y P7_2 como los pines para ser unidos al FTDI2232, eso obliga a seleccionar esos pines como la salida para la UART

Chip_SCU_PinMux(7,1,0,FUNC6); /* P7_1: UART2 TXD */ Chip_SCU_PinMux(7,2,0,FUNC6); /* P7_2: UART2 RXD */

Configurar el Periférico

Como segunda fase, se encuentra la configuración del propio dispositivo

en este caso se deberá

- Inicializar la UART

void Chip_UART_Init(LPC_USART_T *pUART);

- Configurar velocidad de transmisión

Status Chip_UART_SetBaud(LPC_USART_T *pUART,uint32_t baudrate);

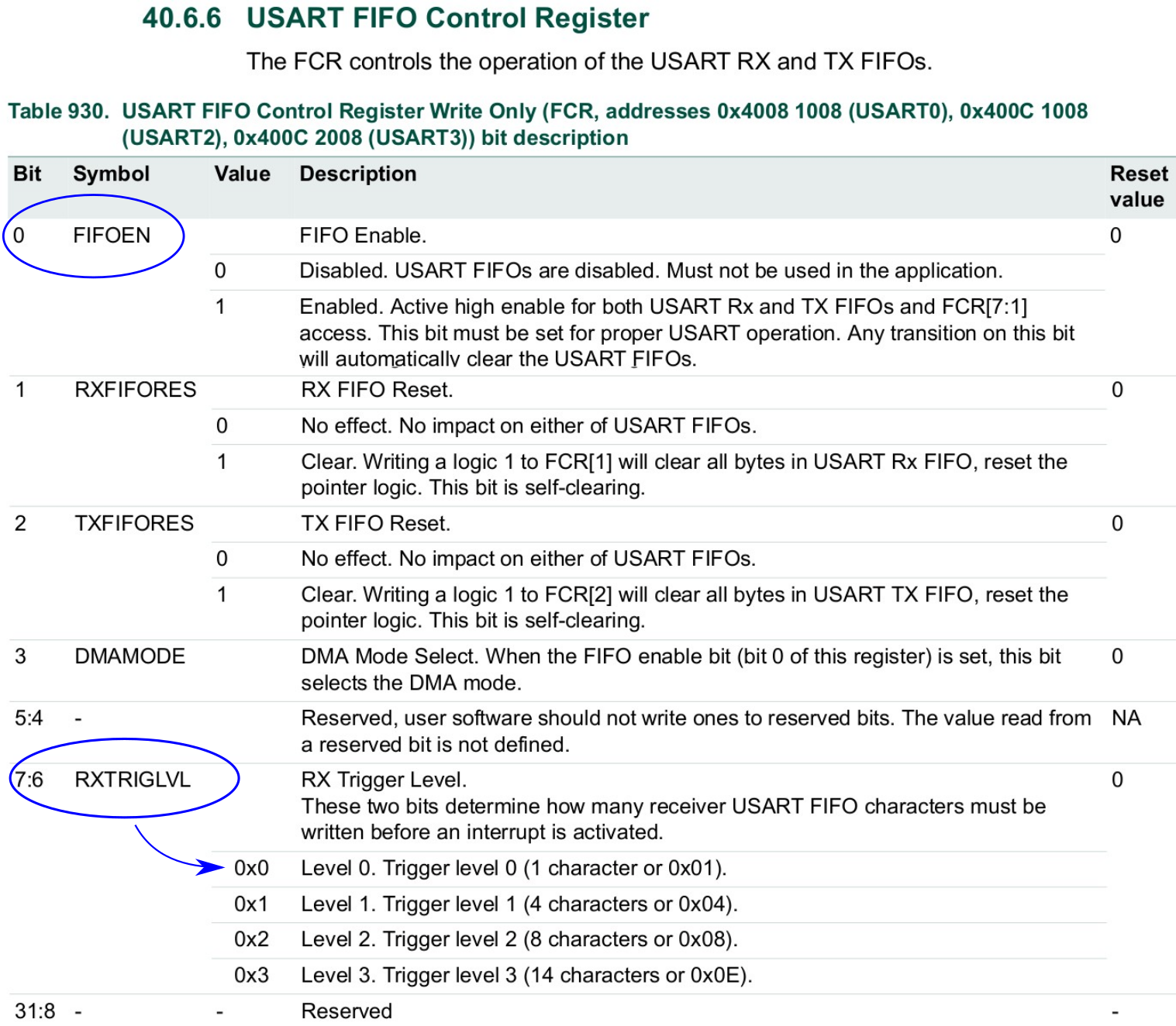

- Configurar la FIFO

STATIC INLINE void Chip_UART_SetupFIFOS(LPC_USART_T *pUART,uint32_t fcr);

Donde fcr se deberá configurar de la siguiente forma UART_FCR_FIFO_EN para habilitar la FIFO y UART_FCR_TRG_LEV0 para generar evento por cada byte recibido

Todas estas acciones se realizan sobre el registro FCR, este registro es utilizado para configurar la FIFO, se muestra a continuación las distintas opciones que posee,(extraído del manual del usuario)

- Habilitar la Transmisión

STATIC INLINE void Chip_UART_TXEnable(LPC_USART_T *pUART);

Uso de la UART

Una vez habilitada y en funcionamiento, se podrá enviar o leer los bytes recibido por medio de dos funciones de la LPCOpen

- Enviar un byte

STATIC INLINE void Chip_UART_SendByte (LPC_USART_T *pUART, uint8_t data);

- Recibir un byte

STATIC INLINE uint8_t Chip_UART_ReadByte (LPC_USART_T *pUART);