Mapeo

Introducción

Estructura básica de buses (Arquitectura Von Neumann)

Dentro de las arquitecturas de microprocesadores, la arquitectura Von Neumann es la mas difundida, en ella, el medio de almacenamiento son los mismos para las variables, dispositivos de entrada salida y memoria de programa.

Esta arquitectura posee tres tipos de buses principales y uno de selección.

Bus de direcciones

Todo dispositivo de memoria o E/S tiene entradas de direcciones que permiten seleccionar una localidad de memoria dentro de él, la cantidad de posiciones dentro del mismo, determina la cantidad de lineas de dirección, así por ejemplo una memoria de 1K posee 10 terminales que permiten seleccionar sus 2^10 = 1024 localidades o casilleros. El microprocesador controla este bus, colocando en él la dirección a leer o escribir, y al igual que la memoria, la cantidad de terminales que posea destinadas a este bus indica la cantidad de localidades que podrá acceder, por ejemplo un microprocesador de 16 terminales, podrá direccionar 2^16 = 65536 localidades distinta de memoria.

Bus de datos

Es el conjunto de terminales para salida o entrada de datos que poseen los dispositivos de memorias o E/S. Estos terminales son los puntos en los cuales se da entrada a los datos para almacenarlos o se extraen para su lectura, un memoria que posea 8 de estos terminales, significa que el ancho del dato leído o almacenado es 8 bits y cada localidad de memoria almacenará esa cantidad de bits, cuando se hace referencia a un dispositivo de almacenamiento, se indica por la cantidad de localidades y el tamaño de cada una, por ejemplo una memoria de 1K x 8 indica que tiene 1024 bytes o 1024 localidades de 8 bits cada una, en cambio otra memoria de 256K x 1 tendrá 262144 localidades de 1 bit cada una.

Bus de control

Todo dispositivos usado en una sistema de buses, cuentan con lineas de control, el caso mas simple es la ROM con generalmente 1 señal de este tipo denominada (OE) output enables o (G) conexión de compuerta, los cuales permites dar salida lógica al bus de datos de la localidad seleccionada por el bus de direcciones. En el caso de la RAM, puede poseer o bien un terminal (R/W) el cual indica a la memoria si se quiere escribir o leer el dato, o bien puede tener dos terminales uno WE o W y OE o G, donde un 0 en el primero escribe el dato en el casillero seleccionado y un 0 en el segundo lee el dato seleccionado al igual que la ROM, en este caso solo puede haber un solo terminal con entrada en 0 o ambas en 1, esta ultima opción, deja a la memoria inactiva y a su bus de dato en alta impedancia.

Bus de selección

Cualquier dispositivo que pueda ser colocado en un bus deberá tener alguna terminal con la función de seleccionar a ese dispositivo, esta señal comúnmente denominada CS, CE o S cuando esta inactiva, deshabilita completamente el dispositivo, permaneciendo en alta impedancia sus salida e impidiendo que se lea o se escriba en él.

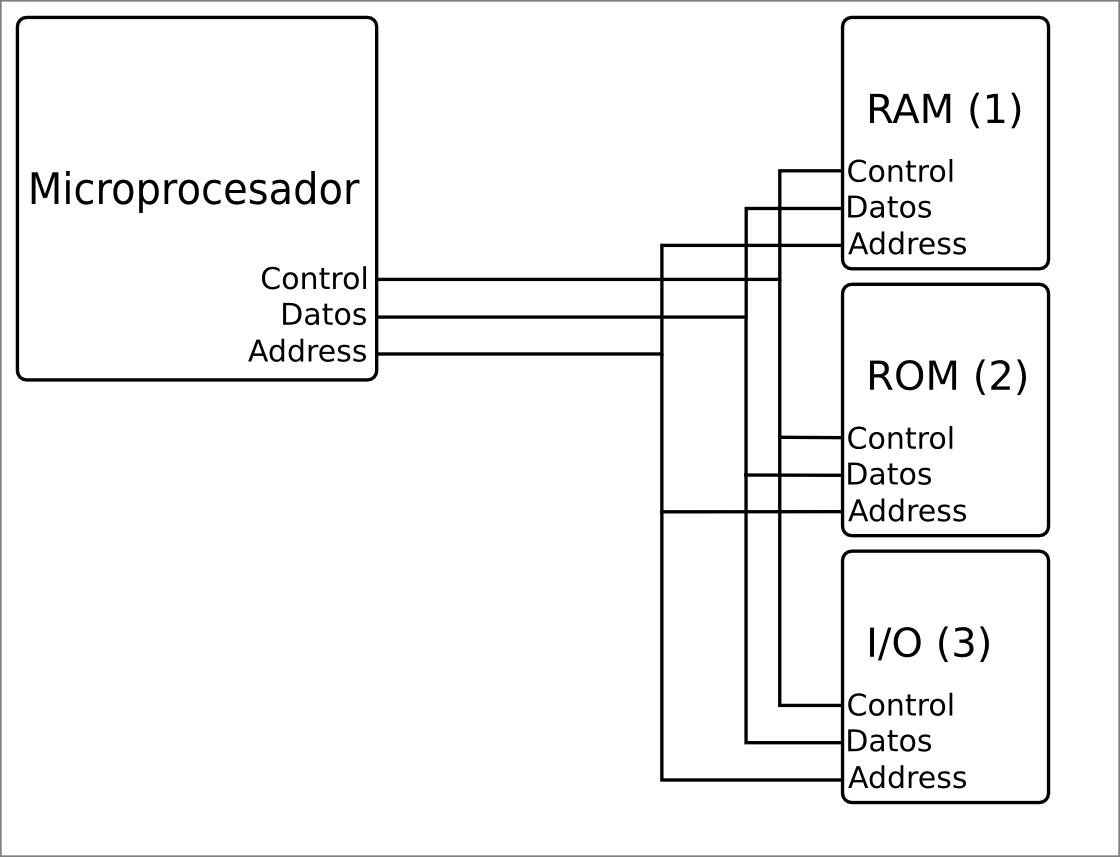

- Figura 1

En la figura se muestra esquemáticamente una arquitectura Von Newman con sus tres buses principales (Direcciones, Datos y Control)

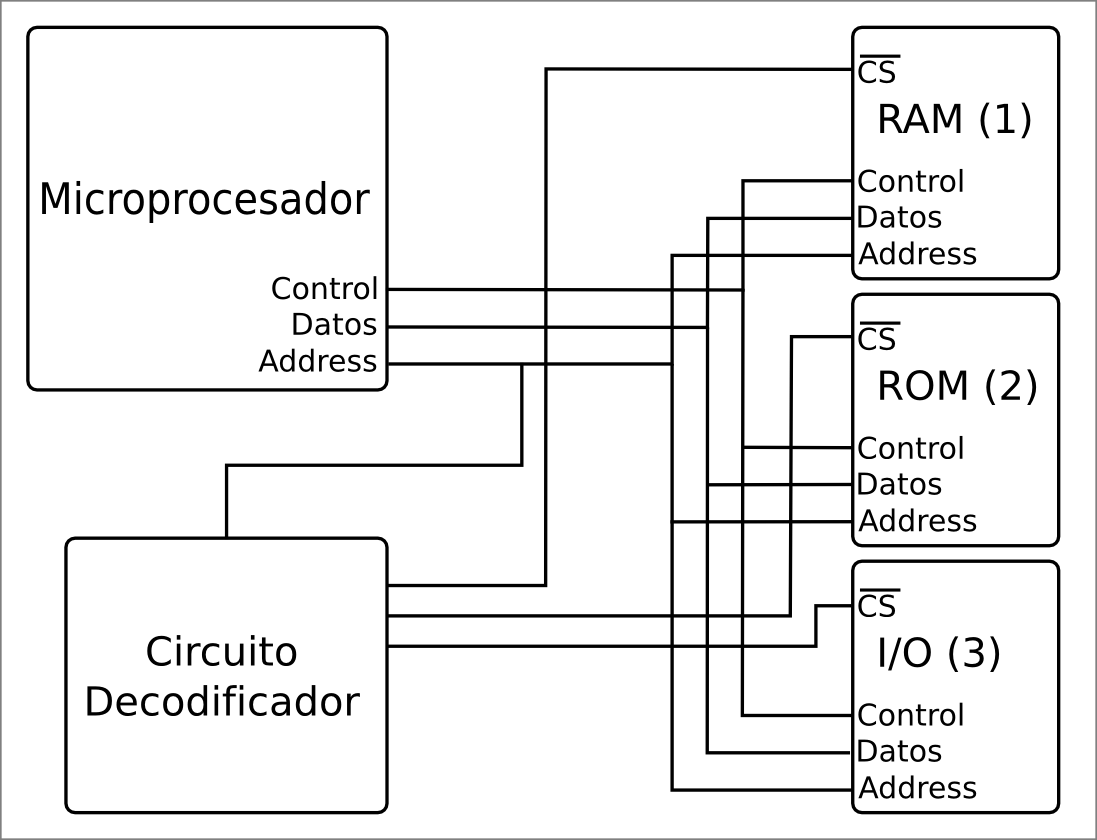

Estructura básica con circuito decodificador o selector.

Como vimos anteriormente, cualquier microprocesador o microcontrolador con salida de direccionamiento externa, posee tres grupos de lineas o buses, el bus de dirección, datos y control. Estas lineas permiten al microcontrolador/microprocesador comunicarse con el exterior enviando la información necesaria para leer o escribir en una posición dada de su mapa de direcciones. Por otro lado, desde el exterior podemos conectar a esas lineas diferentes tipos de memorias y/o dispositivos (RAM, ROM, EPROM, Dispositivos I/O, etc), cada uno con su propio mapa de direcciones que dependerá de su capacidad. Si en un bus de microprocesador, colocamos por ejemplo una memoria RAM de variables y una memoria ROM para el programa, el microprocesador deberá distinguir entre ellas, y a su vez permitir acceder a sus direcciones interna, es en este punto donde entra la tarea del decodificador o selector. El circuito decodificador entonces, nos permite proveer a las memorias y los dispositivos de I/O de una zona exclusiva del mapa de memoria del micro. Además, por el echo de que todo dispositivo a mapear deberá estar contenido en el mapa del microprocesador, este dispositivo debe disponer de una bus de direcciones menor al que provee el micro, esto permite distinguir dos tipos de líneas de direccionamiento.

- Líneas de direccionamiento externas, son las encargadas de diferenciar el dispositivo del resto (dispositivo 1, 2 o 3 de la Figura 2), de esta forma puedo tener varios en un sistema de buses y acceder a uno en especial por medio de estas líneas y un circuito decodificador.

- Líneas de direccionamiento internas, son las que se conectan directamente al dispositivo, este grupo de líneas darán la posición interna del casillero a leer o escribir y corresponden a la parte mas baja de la palabra de direccionamiento.

- Figura 2

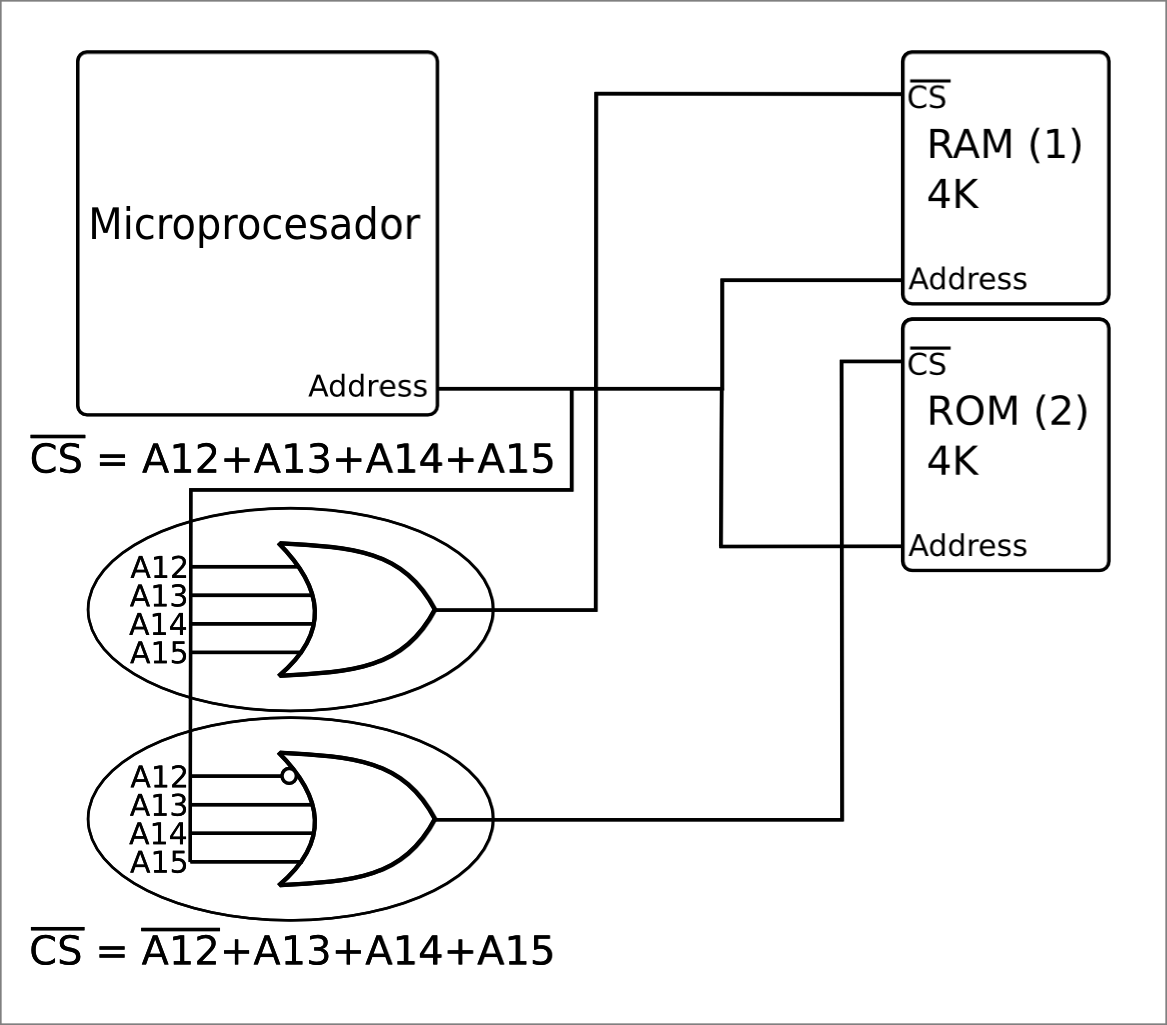

Circuito decodificador de dos memorias

En el siguiente ejemplo, se posee dos memorias, una RAM de 4 Kb y una ROM de 4 Kb, ubicaremos la RAM en la posición mas baja y a continuación la ROM dentro del mapa de un microprocesador genérico de 16 lineas de direccionamiento o 64K casilleros

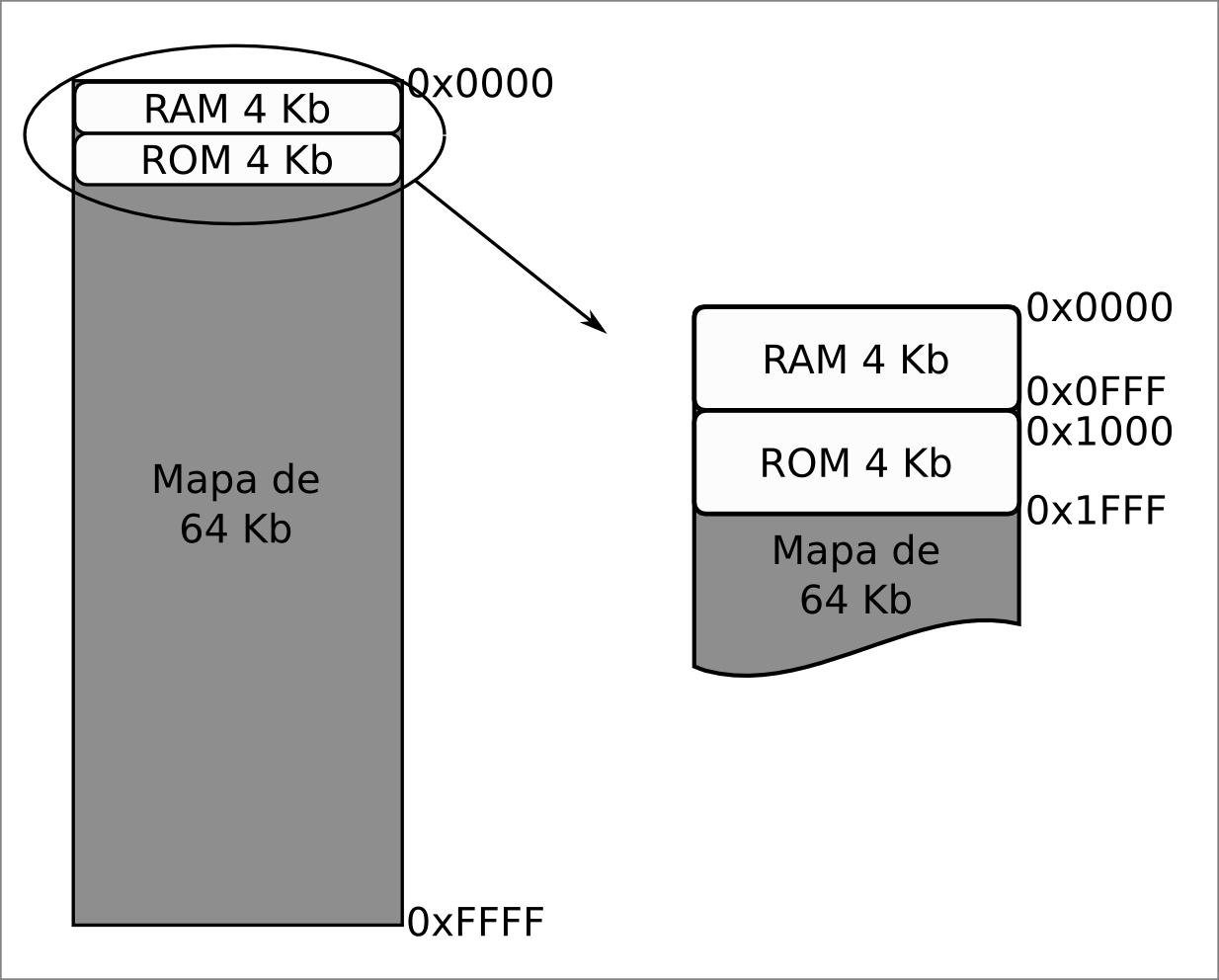

Si realizamos un mapa detallado, calculando las posiciones extremas de cada memoria ( posición inicial y final ), podemos realizar el siguiente diagrama.

Memoria RAM

A15 |

A14 |

A13 |

A12 |

A11 |

A10 |

A9 |

A8 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

hex |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0x0000 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0x0FFF |

Memoria ROM

A15 |

A14 |

A13 |

A12 |

A11 |

A10 |

A9 |

A8 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

hex |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0x1000 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0x1FFF |

La capacidad de cada memoria es de 4 Kb o 4096 casilleros de 8 bits cada uno, para direccionar esa cantidad de memoria necesitamos 12 lineas (2^12 = 4096), si queremos ubicar esta memoria dentro del mapa del microprocesador, el rango de dirección ocupada por la misma deberá comenzar con las 12 lineas menos significativas en 0x000 para direccionar la primera posición de la memoria y terminar con 0xFFF para direccionar la última.

Por otro lado, dado el microprocesador que utilizamos de 16 lineas de direccionamiento, nos quedará 4 lineas correspondiente al direccionamiento externo, estas lineas son las que diferenciará una posición de la RAM con otra de la ROM.

- Figura 3 (se omitieron los buses de datos y control)

Dividimos entonces a las lineas de direccionamiento del microprocesador en:

- Lineas de direccionamiento interna, aquellas que entran directamente a las memorias para direccionar un casillero dentro de ellas, en este caso las 12 lineas menos significativas que entraran a ambas memorias

- Lineas de direccionamiento externa las utilizadas para construir un circuito de mapeo como en la figura 3 donde utilizamos sendas compuertas OR de cuatro entradas como circuito selector.

En el siguiente diagrama, podemos ver la ubicación de las memorias dentro del mapa del microprocesador.

- Figura 4

Controlador de memoria externa (EMC)

Este modulo solo disponible en el 2212 o 2214, provee una interfaz entre el bus del sistema y dispositivos de memoria externa, se pueden configurar hasta 4 bancos de memoria los cuales pueden soportar memoria SRAM,ROM, Flash EPROM, Burst ROM Memory además de dispositivos I/O externo.

Cada uno de estos módulos de memoria pueden ser de 8 16 o 32 bits de ancho y 16MBytes de tamaño.

La ubicación de estos módulos dentro del mapeo del microcontrolador son:

Banco |

Rango |

Configuración del registro |

0 |

8000 0000 - 80FF FFFF |

BCFG0 |

1 |

8100 0000 - 81FF FFFF |

BCFG1 |

2 |

8200 0000 - 82FF FFFF |

BCFG2 |

3 |

8300 0000 - 83FF FFFF |

BCFG3 |

PARA EL ESTUDIO DE ESTE MODULO VER CAPITULO 3 DEL MANUAL DEL ARM