|

Tamaño: 7947

Comentario:

|

Tamaño: 7988

Comentario:

|

| Los textos eliminados se marcan así. | Los textos añadidos se marcan así. |

| Línea 1: | Línea 1: |

| ## page was renamed from PracticoMAPEO2 |

Trabajo Práctico Nro.2 Mapeo

Este practico es opcional y en caso de presentación la misma se debe realizar en KiCad + OpenOffice o Latex , enviando los archivos por mail hasta el martes 22 de Junio.

A continuación puede descargar dos librerías con los esquemáticos del microcontrolador LPC2212/2214, un Microprocesador genérico de 16x8 y algunas memorias genéricas, los cuales les pueden ser útil para realizar los prácticos.

propios.lib: memorias y micro genérico

arm.lib: LPC2212/2214

Ejercicio 1

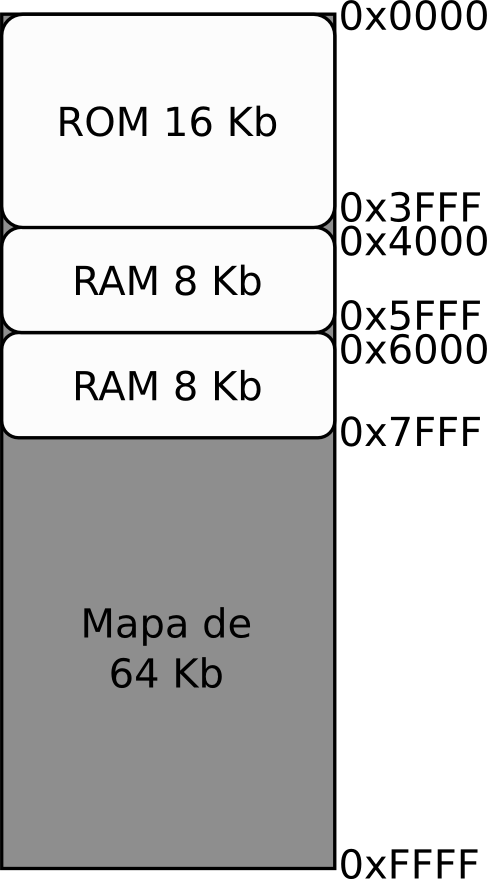

Se dispone de un microprocesador de 64Kb de direccionamiento, se desea implementar:

- 1 CI de memoria RAM de 8 Kb.

- 1 CI de memoria RAM de 8 Kb.

- 1 CI de memoria ROM de 16 Kb.

Partiendo desde la posición 0000h ubicando primero la ROM y a continuación las dos RAM.

Realizamos los mapas de Memoria Reducido y Ampliado con el circuito de decodificación.

Mapa ampliado

Dispositivo |

A15 |

A14 |

A13 |

A12 |

A11 |

A10 |

A9 |

A8 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

hex |

ROM U4 (16 Kb) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0x0000 |

^ |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0x3FFF |

RAM U6 (8 Kb) |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0x4000 |

^ |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0x5FFF |

RAM U5 (8 Kb) |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0x6000 |

^ |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0x7FFF |

Mapa Reducido

Esquemático

Ejercicio 2

Se desea conectar a un microprocesador de 64Kb de direccionamiento, dos memorias una de 4Kb cuya dirección de inicio es 3000h y otra de 2Kb, en la dirección A000h La decodificación deberá ser completa (sin imágenes).

- Realizar el mapa ampliado y reducido, señalando las líneas de decodificación externas e internas.

- Realizar el circuito decodificador completo.

Ejercicio 3

Se desea conectar un microprocesador con un campo de direccionamiento de 64Kb:

- Una banco de memoria ROM de 16Kb formado por CI de 4Kb en la parte baja (a partir de 0000h).

- Una memoria RAM de 24Kb formada por un CI de 16Kb y un CI de 8 Kb en la parte más alta (hasta FFFFh).

Se deberá utilizar un CI 78LS139 para el mapeo de los dos bancos. La decodificación deberá ser completa (sin imágenes).

- Realizar el mapa ampliado y reducido, señalando las líneas de decodificación externas e internas.

- Realizar el circuito decodificador completo.

Ejercicio 4

Cuatro dispositivos ubicados en un mapa de 64 Kb posee las siguientes características:

- posición de comienzo 4000h tamaño 4 Kb.

- posición de comienzo 3000h tamaño 2 Kb.

- posición final 7FFFh tamaño 2 Kb.

- posición de comienzo 8000h tamaño 2 Kb.

¿Cuál es la mínima cantidad de líneas que puedo utilizar en el circuito de mapeo sin que produzcan superposiciones entre los dispositivos? Realizar un mapa detallado tachando las líneas que se eliminen y resaltando las mínimas necesarias.

Ejercicio 5

Utilizando el ejercicio anterior, si quisiéramos modificar los tamaños de cada CI. ¿Hasta que valores podríamos aumentar cada uno?.

Describa el mapa ampliado en esta situación y elimine las lineas posibles sin que se produzcan superposiciones.

Ejercicio 6

En un microcontrolador LPC2114 se debe mapear dos memorias RAM estáticas de 1Mb x 16 cada una en el comienzo del banco 0 configurando este para un bus de datos de 16 bits

1M x 16 equivale a 2Mbytes, es decir 21 lineas de direcciones, como cada casillero de esta memoria es de 16 bits, no usaremos el bit menos significativo del microcontrolador, pero si usaremos las señales BLS que permiten el acceso a la parte alta o baja de los 16 bits.

Realizamos los mapas de Memoria Reducido y Ampliado con el circuito de decodificación.

Mapa ampliado

Dispositivo |

A31:28 |

A27:24 |

A23:20 |

A19:16 |

A15:12 |

A11:8 |

A7:4 |

A3:0 |

hex |

RAM U4 2Mb |

1000 |

0000 |

0000 |

0000 |

0000 |

0000 |

0000 |

0000 |

0x80000000 |

^ |

1000 |

0000 |

0001 |

1111 |

1111 |

1111 |

1111 |

1111 |

0x801FFFFF |

RAM U5 2Mb |

1000 |

0000 |

0010 |

0000 |

0000 |

0000 |

0000 |

0000 |

0x80200000 |

^ |

1000 |

0000 |

0011 |

1111 |

1111 |

1111 |

1111 |

1111 |

0x803FFFFF |

En este mapa, se muestra el rango de cada memoria dentro del mapa completo del micro, la ubicación de arranque del grupo de dos memorias, corresponde a la dirección de comienzo del banco 0, a continuación se muestra un mapa con menos lineas de direcciones, el LPC2212 o 2214 no posee todas las direcciones disponibles solo las primeras 24 lineas salen al exterior, junto con 4 lineas especiales, logrando mapear 4 bancos de 16 Mbyte cada uno

Mapa ampliado de la salida

Dispositivo |

CS0 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

hex |

RAM U4 2Mb |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0x000000 |

^ |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0x1FFFFF |

RAM U5 2Mb |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0x200000 |

^ |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0x3FFFFF |

En este mapa ubicamos las memorias considerando solo las lineas que salen del micro, las cuales son efectivamente las que debemos cablear, incluimos además en las lineas de mapeo externa el CS0 la cual indicará con 0 cuando se esté seleccionando el banco 0.

A continuación, vemos un diagrama del circuito, solo están dibujadas las lineas correspondiente a los buses de datos, control, direcciones y selección, omitiendo las demás ( reloj, interrupciones, alimentación, etc), se presenta en formato pdf por su tamaño

mapeo2.pdf: Esquemático

Ejercicio 7

En el caso anterior, configurado el banco 0 del microprocesador para un bus de datos de 32 bits, realizar el mapeo de ambas memorias.

Ejercicio 8

Mapear en un microcontrolador LPC2214 cuatro memorias RAM estáticas de 1Mb x 8, en el comienzo del banco 0 configurando este para un bus de datos de 16 bits

Ejercicio 9

Mapear en un microcontrolador LPC2214 tres memorias, una memoria de 2M x 8, una de 1M x 16 y una última de 512K x 32, cada memoria se dispone en bancos separados y ubicada cada una al comienzo de los mismos.

Ejercicio 10

Mapear en un microcontrolador LPC2214 dispositivos de memorias, dos de 1M x 8 y una de 512K x 16, las mismas se ubicarán en forma contigua en el banco 0 y sin imágenes, ubicando el conjunto de las dos memorias de 1M x 8 como una sola de 1M x 16, formando junto con la restante, un solo bloque de 1,5 M x 16