PLL (PHASE LOCKED LOOP)

El PLL o Lazo Enganchado de Fase, es básicamente un sistema de lazo cerrado de frecuencia, se basa en un control de fase que mide la diferencia entre una frecuencia de entrada patrón y la frecuencia de un oscilador controlado, de esta forma el error de fase actuará sobre el oscilador de frecuencia variable modificando su salida acercándola a la frecuencia del oscilador patrón.

Intercalando divisores podemos generar frecuencias superiores a la frecuencia patrón, este uso es el dado por el microcontrolador, permitiendo de este modo elevar la frecuencia desde un cristal de 10 a 20 Mhz a 10 a 60 Mhz de frecuencia interna.

Tabla de las distintas frecuencias que intervienen en el PLL

Nombre |

Descripción |

Rango de operación |

Fosc |

Frecuencia del oscilador externo |

10 a 20 Mhz |

Fcco |

Frecuencia del oscilador controlado por corriente |

156 Mhz a 320 Mhz |

cclk |

Frecuencia interna del microcontrolador |

10 a 60 Mhz |

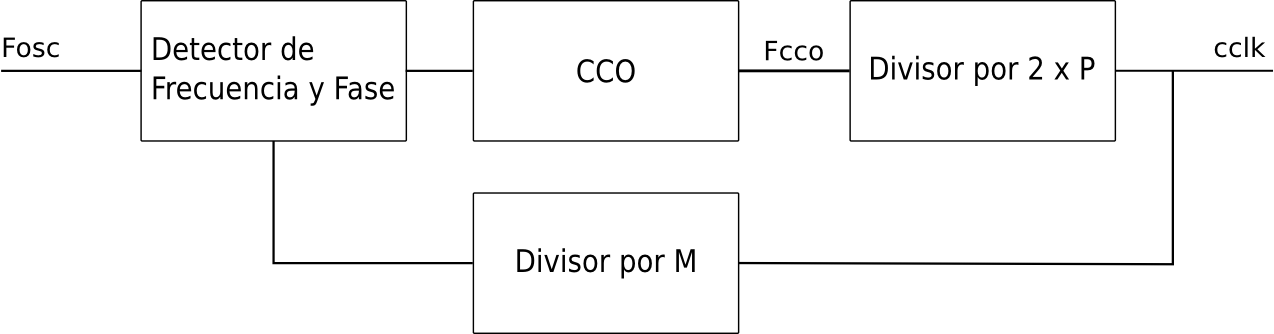

En la figura se muestra el diagrama simplificado del PLL aplicado al microcontrolador, como vemos, tenemos dos divisores que permiten configurar al dispositivo a una frecuencia interna para una frecuencia dada del cristal externo.

Por un lado tenemos el multiplicador M, este modulo divide la frecuencia interna por un entero y este valor es comparado con la frecuencia externa, el echo de llamarlo multiplicador, se debe a que del punto de vista de la frecuencia interna, ésta será la frecuencia del oscilador externo multiplicada por M

Si por ejemplo tenemos un oscilador de 10 Mhz y este divisor lo configuramos a 6, entonces el oscilador se acomodará para dar una salida a la frecuencia interna de 60 Mhz.

El divisor P, es utilizado para configurar la frecuencia del oscilador interno a un rango dado por el fabricante, en este caso 156 Mhz a 320 Mhz, una vez establecido la frecuencia que queremos mediante M, establecemos P para que el OCC funcione en el rango en el cual fue diseñado, siguiendo el ejemplo con P = 2 la frecuencia del OCC es 60 * 2 * 2 = 240Mhz el cual es una frecuencia valida.

Veamos ahora el calculo para un oscilador externo de 14,7456 Mhz

Establecemos M = 4

cclk = M * Fosc = 4 * 14,7456 = 58,9824

ahora P deberá ser 2

Fcco = cclk * 2 * 2 = 58,9824 * 2 * 2 = 235,9296 Mhz

Queda para este ejemplo entonces M = 4 y P = 2

Configuración del PLL en el ARM

La configuración del PLL se realiza mediante los siguientes registros

Dirección |

Nombre |

Descripción |

Acceso |

0xE01FC080 |

PLLCON |

Registro de Control, permite la habilitación del PLL, las modificaciones realizadas no tienen efecto hasta que se realiza la secuencia de actualización. |

R/W |

0xE01FC084 |

PLLCFG |

Registro de Configuración, establece los divisores P y M, las modificaciones realizadas no tienen efecto hasta que se realiza la secuencia de actualización |

R/W |

0xE01FC088 |

PLLSTAT |

Registro de STATUS, informa sobre el estado del PLL y los divisores que se están usando en este momento |

R |

0xE01FC08C |

PLLFEED |

Registro FEED o de habilitación del PLL, escribiendo una secuencia de caracteres en este registro (secuencia de actualización) se habilitan las modificaciones echas en PLLCON y PLLCFG |

W |

Registro de Control

El PLLCON es un registro de 8 bits de los cuales solo dos bits tienen función.

- bit 0 (PLLE) es el que habilita el PLL para que se enganche a la fase, valor de reset = 0.

- bit 1 (PLLC) en el momento que este bit y PLLE están en 1 y luego de una secuencia de actualización, el PLL pasa a ser el oscilador del microcontrolador, valor de reset = 0.

- bit 2 - 7 son reservados y no deben ser escrito con 1.

La secuencia correcta es: establecer primero el PLL y que este se enganche a la fase (PLLE = 1 ) y luego activar el PLL (PLLE = 1 y PLLC = 1)

Las diferentes combinaciones de los bits PLLC y PLLE pueden mostrarse en la siguiente tabla

PLLC |

PLLE |

Estado del PLL |

0 |

0 |

el PLL es desactivado y desconectado, el microcontrolador funciona con el reloj externo conectado en forma directa |

0 |

1 |

el PLL es activado, el PLL comienza a funcionar, pudiendo ser conectado cuando la fase se enganche (PLOCK = 1) |

1 |

0 |

igual que 0 0, esto previene que se conecte el PLL sin ser habilitado previamente |

1 |

1 |

el PLL está activo y es el oscilador interno del microcontrolador |

Registro de Configuración

Como se describió anteriormente este registro de 8 bits, posee los valores de P y M

- MSEL bit 0 a 4 valor del multiplicador M, donde para un valor M = 1 tenemos MSEL = 00000, para M = 2 MSEL = 00001 y así hasta M = 32, si bien este sería el valor mas alto, los valores posibles son de 1 a 6, dada la menor frecuencia del oscilador externo ( 10 Mhz) y el mayor valor del oscilador interno ( 60 Mhz )

- PSEL bit 5 a 6 el divisor P se configura de la siguiente forma:

PSEL bits |

Valor de P |

00 |

1 |

01 |

2 |

10 |

4 |

11 |

5 |

- bit 7 es un bit reservado y no se debe escribir 1

Registro de STATUS

Provee los valores actuales del PLL, estos valores pueden ser distintos de los guardados en los registros de control y configuración, solo la secuencia de actualización hace efectivo los cambios de esos registros al PLL y mientras que esta no se produzca, los valores internos del PLL no se modifican.

- bits 0 a 4, MSEL valores actuales del multiplicador M

- bits 5 a 6, PSEL valores actuales del divisor P

- bits 7, reservado

- bits 8, PLLE valores actuales del PLLE

- bits 9, PLLC valores actuales del PLLC

- bits 10,PLOCK, refleja el estado del lazo del PLL, es decir si el PLL ya se encuentra enganchado en fase, este bits es muy importante porque permite decidir cuando se está en condiciones de que el PLL pase a ser el oscilador del microcontrolador.

- bits 11 a 15 reservados.

Interrupción

El bit PLOCK puede ser conectado al controlador de interrupciones, lo que permite activar el PLL y continuar haciendo otra cosa, en el momento en que se enganche la fase (PLOCK = 1) se genera una interrupción, la cual coloca al PLL con entrada del oscilador interno y desactiva la interrupción.

PLL Feed Register o registro de actualización

El registro de actualización es utilizado para generar la secuencia de actualización, esta secuencia es para registrar los cambios que se realicen en el PLL, esto evita cualquier error de escrituras accidentales en los registros de configuración.

La secuencia son dos caracteres que se escriben en este registro en ciclos de bus consecutivos, estos caracteres son 0xAA y 0x55, esto significa que la interrupción debe ser desactivada en este período de configuración, si los caracteres no son los correctos, o alguna de las anteriores condiciones no se cumple, los cambios en PLLCON o PLLCFG no se realizan.

Programa de configuración

Este programa realizado en assembler se debe intercalar en el STARTUP y permite configurar un PLL en esta caso para que oscile a 58,9824 Mhz partiendo de un cristal que lo hace a 14.7456 Mhz

...........

...........

...........

/*

* Establecer PLL

* -----------------------------------------------------------------------------

*/

@ Se usa r0 para cargar la posición del primer registro del PLL

@ para acceder luego a los demás registros se utilizará esta dirección como base mas un offset

ldr r0, PLLBASE

@ PLLCFG = PLLCFG_VALUE se configura el divisor D y el multiplicador P según una constante

mov r3, #PLLCFG_VALUE

str r3, [r0, #PLLCFG_OFFSET]

@ PLLCON = PLLCON_PLLE se configura el PLLE = 1 y PLLC = 0 esto es para activar el PLL

mov r3, #PLLCON_PLLE

str r3, [r0, #PLLCON_OFFSET]

@ PLLFEED = PLLFEED1, PLLFEED2

@ se realiza la secuencia de actualización para hacer efectivos los cambios

mov r1, #PLLFEED1

mov r2, #PLLFEED2

str r1, [r0, #PLLFEED_OFFSET]

str r2, [r0, #PLLFEED_OFFSET]

@ repetir mientras ((PLLSTAT & PLLSTAT_PLOCK) == 0)

@ este bucle se realiza hasta que se enganche la fase

pll_loop:

ldr r3, [r0, #PLLSTAT_OFFSET]

tst r3, #PLLSTAT_PLOCK

beq pll_loop

@ PLLCON = PLLCON_PLLC||PLLCON_PLLE

@ una vez enganchada la fase se procede a configurar el PLL como oscilador del microcontrolador

mov r3, #PLLCON_PLLC||PLLCON_PLLE

str r3, [r0, #PLLCON_OFFSET]

@ PLLFEED = PLLFEED1, PLLFEED2

@ una nueva secuencia de actualización hace efectivo el cambio y ahora el PLL es el oscilador del sistema

str r1, [r0, #PLLFEED_OFFSET]

str r2, [r0, #PLLFEED_OFFSET]

...........

...........

...........

PLLBASE: .word 0xE01FC080

/*

* las constantes de 8 bits son usadas como valores inmediatos y offset

*/

@ PLL configuration

.equ PLLCON_OFFSET, 0x0

.equ PLLCFG_OFFSET, 0x4

.equ PLLSTAT_OFFSET, 0x8

.equ PLLFEED_OFFSET, 0xC

.equ PLLCON_PLLE, (1 << 0)

.equ PLLCON_PLLC, (1 << 1)

.equ PLLSTAT_PLOCK, (1 << 10)

.equ PLLFEED1, 0xAA

.equ PLLFEED2, 0x55

@ el valor del CFG corresponde a un M = 4 MSEL = 00011 y P = 2 PSEL = 01

.equ PLLCFG_VALUE, 0x23

@ configuracíon del PLL para cristal de 14,7456 Mhz